快訊

- 幕後/藍稱鄭麗文內部課程沒批趙少康、酸馬英九 與會學員:明明有講,怎敢澄清?

- 川普:向習近平提了黎智英案 「他說這很棘手」

- 【有片】青森市中心驚現熊蹤 跑進商業大樓遭擊斃

- 快訊/日相高市與川普通電話 「川習會曾談到日本」

- 指部分政黨媒體藉「川習會」炒作疑美、疑台論 林佳龍批:無助於國家團結與安全

- 台中驚見廢土山!大肚地主清運費1.38億 怒轟「2年查不出主嫌」

- 擎天崗野戰!官方直播全程放送……警察揪出情侶身分1罪偵辦

- 商借國王專機、人員只帶隨身行李 紐時:賴清德訪史瓦帝尼「與中國高空貓捉老鼠」

- 【更新】員工扮鬼遭勒頸亡 「邏思起子」2負責人共40萬交保

- 王彥程5局狂飆8K第4勝終於到手!三振數寫旅韓生涯新高

- 00403A信仰不滅! 淨值破發、四天規模爆衝翻倍 已進場買股1191億元

- 快訊/川普:未就台灣問題對習近平作出任何承諾 將很快就對台軍售作決定

- 游淑貞邀花蓮國中校長主任到吉安領包中御守給考生 陳培瑜轟:拿祝福包裝違反行政中立

- 鄭麗文批趙少康難溝通、馬英九身體差、前主席敗黨 趙:國民黨真「深慶得人」

- 花蓮暴雨!佛祖街、阿陶莫部落又淹了 公所收容20人

- 三星罷工損失上看2兆 資方溫情喊「將工會視為家人」籲談判

- 川習會之際荷姆茲海峽再現緊張 一船被扣一船被擊沉

- Toyz獄中出招!挨「超派鐵拳」被迫停工 再告超哥求償205萬

- 柯案二審備戰!高院先祭「柯文哲條款」防法官落跑 貪污庭12人請調添變數

- 南韓青瓦台:日相高市下週訪問李在明故鄉、舉行雙邊會談

【下一個CoWoS】晶圓、封測、面板廠競相投入!一文看懂「FOPLP」夯什麼

2024-07-07 07:10 / 作者 戴嘉芬

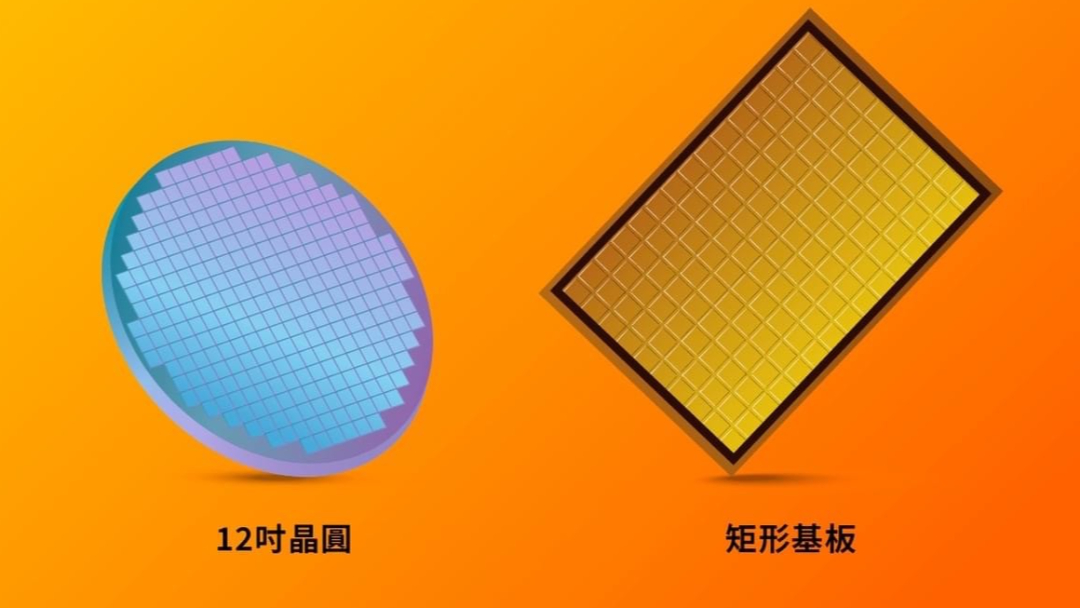

FOPLP面板級扇出型封裝採矩形基板(右),邊緣可利用率比晶圓(左)來得高,可藉此降低製程成本。翻攝自SEMI國際半導體產業協會FB

AI 應用大爆發!CoWoS 產能吃緊,晶圓廠和封測廠基於成本與效能考量,正在尋求其他先進封裝技術,最近火紅的 FOPLP 面板級扇出型封裝(Fan out Panel-level Packaging)正是被點名的關鍵技術,不只吸引台積電、三星、英特爾三大廠相繼投入,AI 晶片巨擘輝達更透露將在2025年於GB200率先採用面板級扇出型封裝技術,成為 FOPLP 前進 AI 應用的發展契機。而國內面板大廠群創率先切入 FOPLP,成功從面板製造業跨足到半導體封裝領域。先前日媒報導,台積電正在與設備、材料商合作,共同投入FOPLP技術開發。此項技術與晶圓級封裝相比,能提升邊緣利用率,藉此容納更多晶片。對此,台積電僅表示,「密切關注先進封裝的進展和發展,包括面板級封裝技術在內。」

日月光投控營運長吳田玉日前受訪表示,面板級封裝分成很多種,大面板具備經濟效益和低成本的優勢,朝高階、長線方向佈局,分別都有鎖定的客群。他以「人形機器人」舉例,它們的手指會動,因此必須具備感測器、微控制器、記憶體、電源管理IC等,這就可以採用面板級扇出封裝。吳田玉認為,先進封裝技術有愈來愈多廠商參與,這代表市場接受度愈高,他以正面看待市場競爭。

日月光投控營運長吳田玉以「人形機器人」為例,裡面的IC種類眾多,就很適合採用面板級扇出封裝技術。日月光提供

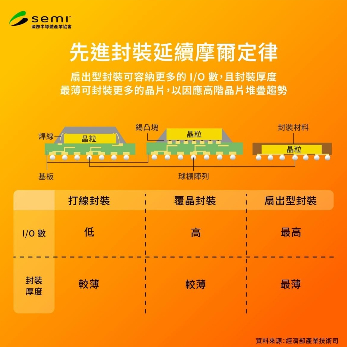

工研院產科國際所經理范哲豪在近日研討會指出,AI、HPC 需求推動半導體封裝技術朝高密度互連發展。封裝業基於成本、效能、微型化等考量,已衍生出多種封裝型態來滿足不同應用領域,除了2.5D/3DIC等封裝技術外,在成本與效能的優勢下,也驅動扇出型封裝延伸至面板級載體,FOPLP這種高階封裝技術將是大廠未來的布局方向;因其電阻值較低,改善電氣與散熱特性,可進一步提升封裝後元件整體效能。

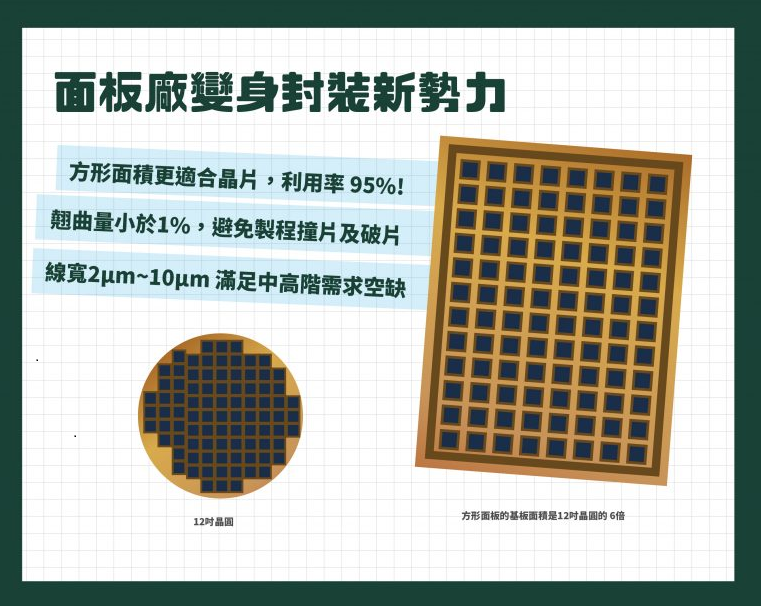

負責研究封測產業的產科所分析師張筠苡也補充道,FOPLP技術使用方型面板代替傳統圓形晶圓(Wafer-level Packaging)作為扇出封裝過程中的載體。在良率條件相同的前提下,其可容納的封裝單位超過圓形晶圓,讓面積使用率從69%提升至84%,進而增加產量,是此技術最大優勢。面板單位面積封裝成本約可比圓形晶圓降低10%~15%,而隨著尺寸增加,成本降幅會更加明顯。

「面板級扇出型封裝技術」無論體積與效能,相較過往的封裝技術皆有大幅提昇。截自經濟部產業技術司官網

比較上述兩種技術,張筠苡認為,FOWLP 扇出晶圓級封裝(Fan out Wafer-level Packaging)仍是扇出型封裝的主流載體,比重高於90%,年複合成長率為12.1%。而FOPLP扇出面板級封裝則能提供高性能、低成本的解決方案,被認為是利基市場,成長潛力不容忽視,將以22.1%年複合成長率快速成長。

再提到FOPLP的規格,她則表示,業界並沒有統一的標準尺寸,目前FOPLP面板尺寸以510x515mm、600x600mm為常見規格,並朝更大面積發展,這是為了極大化生產效率和降低成本。其次,線寬線距則朝2微米以下發展,以迎合5G、AI需求,朝向高I/O數連接的手機AP應用。

工研院分析師張筠苡認為,隨著先進製程遇微縮瓶頸,晶圓廠推動先進封裝技術,以實現一站式服務。而專業封測代工廠則集中在Fan-Out及2.5D封裝技術。戴嘉芬攝

目前布局FOPLP的面板廠以群創最為積極!群創活化3.5代面板廠轉為FOPLP產線,跨入封裝業務,已開發出620x750mm²大尺寸玻璃基板,具備細線寬2μm~10μm(2微米至10微米)的中高階半導體封裝,且沿用舊廠7成的面板設備,藉此提升成本競爭力與毛利率。

媒體報導,群創FOPLP初期產能已被兩大歐系客戶NXP、意法半導體預訂,規劃本季量產出貨。今年將邁入第二期擴產階段,將FOPLP產能擴大數倍,估計未來最大月產能可達1.5萬片,成功從面板生產跨足到半導體先進封裝領域。

張筠苡也解釋Fan-out(扇出型封裝)技術的特性。它一開始採用的晶圓級封裝,是將整塊晶圓先做封裝再切割成分離小晶片,並將測試良好的晶片放在載體上進行封膠,此技術不需要導線架和基板,有助於縮小封裝尺寸,但同時也面臨應力、對齊、切割等挑戰。

其次,Fan-out封裝允許基片之I/O連接點透過RDL重分布層進行擴展。因此,佈局範圍就不會僅限於晶片面積的大小,而是從這個晶片中央的凸塊陣列 透過重分布層擴展至整個封裝體的邊緣,可有效提升晶片的連接密度。故Fan-out封裝就成為高I/O密度應用下的一個理想選擇。

半導體業藉由先進封裝技術來延續摩爾定律,扇出型封裝的厚度最薄,可封裝更多晶片。翻攝自SEMI國際半導體產業協會FB

工研院預估扇出型封裝市場近5年(2023~2028)年複合成長率達12.4%,到了2028年,市場整體規模將達到37.6億美元。「主要應用來自於消費性電子領域,加上全球環保減碳意識興起,驅動移動載具在自動化、智慧化、電動化需求,預估車載應用將會迎來一波成長空間。」張筠苡說。

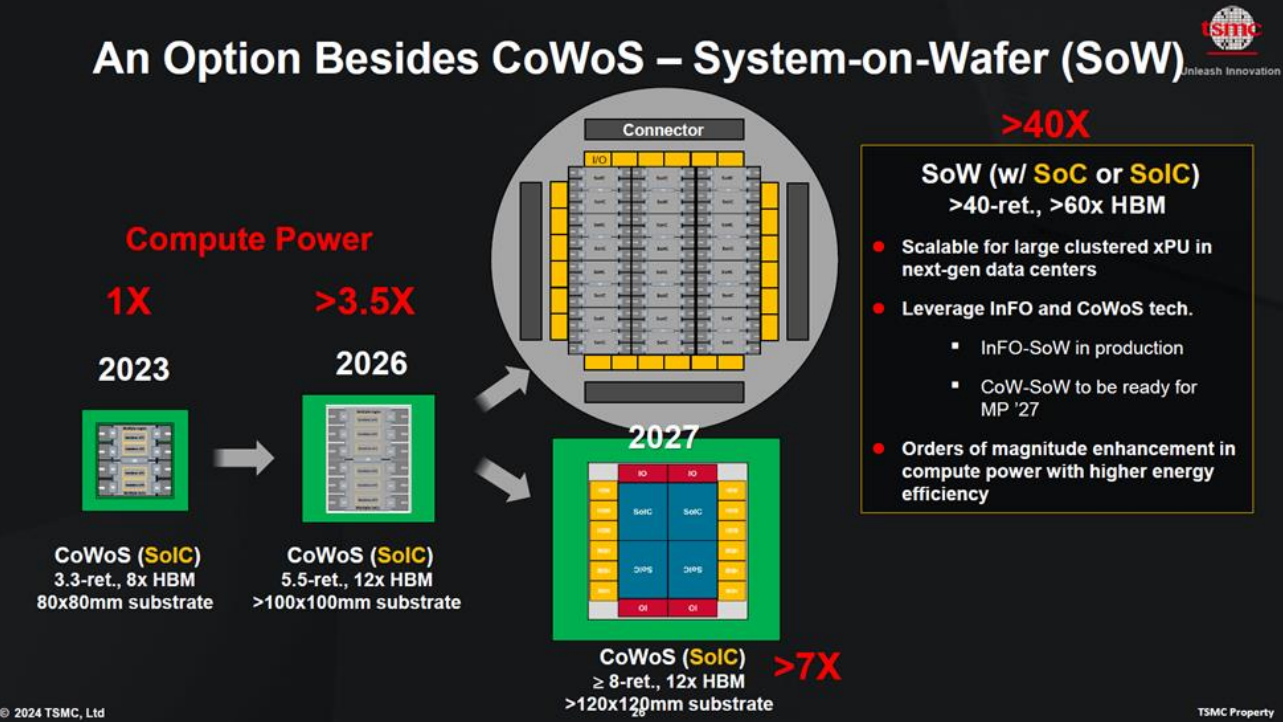

目前台積電扇出型封裝技術包括InFO-POP及今年剛發表的InFO-SoW系統級晶圓。台積電表示,目前採用InFO技術的系統級晶圓已量產,而採用CoWos技術的系統級晶圓,能整合SoC或SoIC、HBM及其他元件,預計2027年開始量產。

台積電今年發表系統級晶圓SoW技術,採用CoWos技術的系統級晶圓預計2027年開始量產。取自TSMC

研調機構TrendForce指出,台積電在2016年開發出InFO(整合扇出型封裝)的FOWLP技術,並應用於iPhone 7手機所使用的A10處理器後,專業封測代工廠(OSAT)業者競相發展FOWLP及FOPLP技術,以提出單位成本更低的封裝解決方案。自今年第二季起,超微、輝達等晶片業者積極接洽台積電及封測業者,洽談以FOPLP技術進行晶片封裝,帶動業界對FOPLP技術的關注。

TrendForce進一步指出,從FOPLP技術對封測產業發展的影響面來看,第一,封測代工業者可提供低成本的封裝解決方案,提升在既有消費性IC的市占,甚至跨入多晶片封裝、異質整合的業務。其次,面板業者可跨入半導體封裝業務。第三,晶圓廠及封測業者可壓低2.5D封裝模式的成本結構,甚至藉此進一步將2.5D封裝服務自既有的AI GPU市場推廣至消費性IC市場。第四,GPU業者可擴大AI GPU的封裝尺寸。

TrendForce認為,FOPLP技術的優勢及劣勢、採用誘因及挑戰並存。主要優勢為低單位成本及大封裝尺寸,惟技術及設備體系尚待發展,技術商業化的進程存在高度不確定性,預估目前FOPLP封裝技術發展在消費性IC及AI GPU應用的量產時間點,可能分別落於2024年下半年至2026年,以及2027~2028年。

最新more>

熱門more>

- 章子怡確定不演!李安新片《金山》卡司曝光 《3體》台灣女星加盟

- 台北密室逃脫「女員工扮鬼遭繩勒」 搶救5天不治!家屬淚提3大訴求:她不是道具

- 00403A跌破掛牌價! 淨值降至9.93元 本週追高全套牢 造市商套利大贏 投資人愈跌愈買

- 擎天崗野戰!官方直播全程放送……警察揪出情侶身分1罪偵辦

- 悚!清大台積館女學生墜樓亡

- 袁立本、田博仁今年剛升官 台積電中生代接班梯隊論壇初亮相

- 張凌赫情史「只和她交往過」 白鹿1句話遭網暴!三天掉10萬粉

- 鄭麗文批趙少康難溝通、馬英九身體差、前主席敗黨 趙:國民黨真「深慶得人」

- 【技術論壇懶人包】台積電高層:半導體市場今年將超越1兆美元 全球最新製程進度曝光

- 中天主播馬德淪共諜3罪起訴 收紅錢金流大曝光!海陸軍全淪陷